HDL Works

- Home

- Products

- Sales

- Support

- Company

- HDL Corner

HDL Works

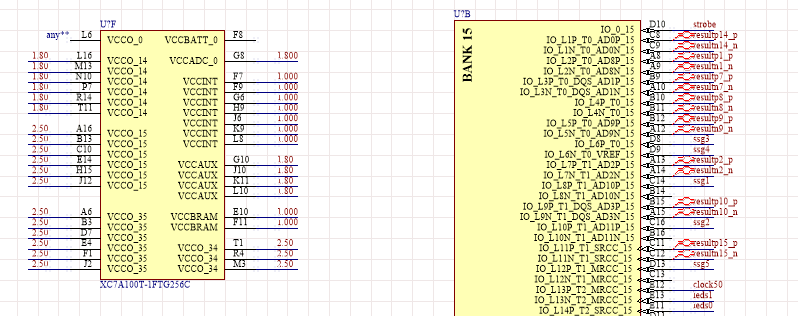

The schematic update interface allows you to add wires (and IO ports) to the symbols of an FPGA instantiated on different schematic pages based on the FPGA pin file, design constraints, or a CVS file. The interface can be used for both initial wiring of components or to update existing schematics because of changes in the pin assignments of the FPGA. For power and ground pins you can add a wire or place a note about the required voltage near the pin. The available options depend on the selected schematic capture system.

Automatically adding wires to components of a large FPGA saves valuable time and guarantees equal signal names in both design environments.

This release supports Altium Designer and Cadence Allegro.

HDL works has developed an IO Checker extension for Altium Designer. Using the

extension you can create or update an IO Checker project or wire specific parts

of FPGA component based on IO Checker data. More information on the extension

can be found of the Altium page.

Constraints update and generation

![]()

FPGA symbols

FPGA symbols

Copyright © 2004 - 2026 HDL Works